Thomas Sohmers is the founder and CEO of REX Computing

In this video, Thomas Sohmers from Rex Computing presents: The REX Neo Architecture: An energy efficient new processor architecture.

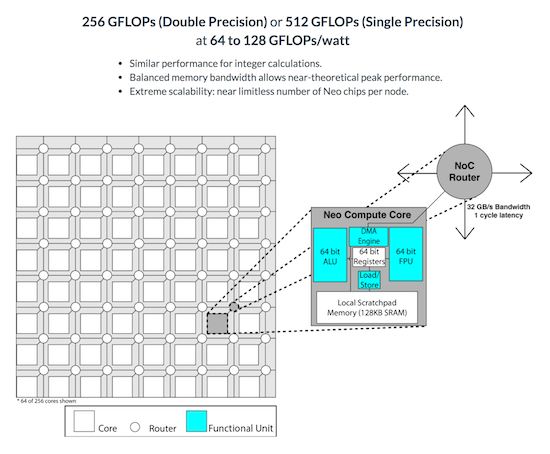

“REX Computing is a fabless semiconductor startup developing the a new processor architecture targeting a 10 to 25x energy efficiency improvement in high performance computing and digital signal processing domains. The REX Neo architecture gains its performance and efficiency improvements with a reexamining of the on chip memory system, but retains general programmability with breakthrough software tools. With a team of four and less than $2 million, REX has taken a design concept to reality in under a year with a 16 core processor manufactured on a modern TSMC 28nm process node. With this test silicon, REX is breaking the traditional semiconductor industry idea that it takes large teams along with tens or even hundreds of millions of dollars to deliver a groundbreaking processor. This talk will feature an overview of the Neo ISA, microarchitecture review of the first test silicon, along with a live hardware/software demonstration.”

Thomas Sohmers is the founder and CEO of REX Computing, where he also leads architectural development of the Neo architecture. He started off as a research affiliate at the MIT Institute for Soldier Nanotechnologies when he was 13 for three years as both an end user of HPC systems, and later transitioned into designing and building them at the lab. This experience led to starting REX Computing in 2013 as a recipient of Peter Thiel’s 20 Under 20 Fellowship, with the goal of an order of magnitude improvement in energy efficiency in the high performance computing domains. Thomas has been featured on Forbes’ 30 under 30 list and was a former project lead for the Open Compute Project HPC Group.

Sign up for our insideHPC Newsletter

Looks like a stripped-down version of a CoherentLogix HyperX chip. The drawing shows 16*16 cores when in fact they only implemented 4*4 so far in 28nm. Crosstalk, leakage, etc. is going to be tough to manage with a handful of people when they move to 14nm or below. They’re also likely to run into a lot of workload scheduling issues when they scale up to 16*16 cores. How about software tools?