In this video from the Disruptive Technologies session at the 2015 HPC User Forum, Peter Hopton from Iceotope presents: ExaNeSt technology: Targeting Exascale in 2018.

“ExaNeSt will develop, evaluate, and prototype the physical platform and architectural solution for a unified Communication and Storage Interconnect and the physical rack and environmental structures required to deliver European Exascale Systems. The consortium brings technology, skills, and knowledge across the entire value chain from computing IP to packaging and system deployment; and from operating systems, storage, and communication to HPC with big data management, algorithms, applications, and frameworks. Building on a decade of advanced R&D, ExaNeSt will deliver the solution that can support exascale deployment in the follow-up industrial commercialization phases. Using direction from the ETP4HPC roadmap and soon-available high density and efficiency compute, we will model, simulate, and validate through prototype, a system with:

- High throughput, low latency connectivity, suitable for exascale-level compute, their storage, and I/O, with congestion mitigation, QoS guarantees, and resilience.

- Support for distributed storage located with the compute elements providing low latency that non-volatile memories require, while reducing energy, complexity, and costs.

- Support for task-to-data sw locality models to ensure minimum data communication energy overheads and property maintenance in databases.

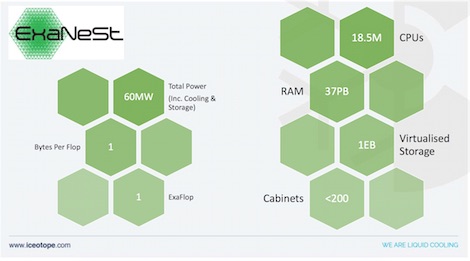

- Hyper-density system integration scheme that will develop a modular, commercial, European-sourced advanced cooling system for exascale in ~200 racks while maintaining reliability and cost of ownership.

- The platform management scheme for big-data I/O to this resilient, unified distributed storage compute architecture.

- Demonstrate the applicability of the platform for the complete spectrum of Big Data applications, e.g. from HPC simulations to Business Intelligence support.

All aspects of ExaNeSt will be steered and validated with the first-hand experience of HPC applications and experts, through kernel turning and subsequent data management and application analysis.”

All aspects of ExaNeSt will be steered and validated with the first-hand experience of HPC applications and experts, through kernel turning and subsequent data management and application analysis.”

See more talks from the HPC User Forum

In related news, the HPC User Forum has posted their Agendas for upcoming meetings in Europe:

- GENCI will host the HPC User Forum in Paris Oct. 12-13. The Agenda includes speakers from Airbus, GENCI, Renault, and NASA. The meeting is free to attend. Register now.

- LRZ will host the HPC User Forum in Munich Oct 15-16. The Agenda includes speakers from LRZ, CSCS, DKRZ, Paypal, and the Gauss Centre for Supercomputing. The meeting is free to attend. Register now.