Berkeley Lab recently hosted the fourth annual X-Stack PI event, where X-Stack researchers, facilities teams, application scientists, and developers from national labs, universities, and industry met to share the latest developments in X-Stack application codes. “X-Stack was launched in 2012 by the U.S. Department of Energy’s Advanced Scientific Computing Research program to support the development of exascale software tools, including programming languages and libraries, compilers and runtime systems, that will help programmers handle massive parallelism, data movement, heterogeneity and failures as the scientific community transitions to the next generation of extreme-scale supercomputers.”

Video: Optimizing Applications for the CORI Supercomputer at NERSC

In this video from SC15, NERSC shares its experience on optimizing applications to run on the new Intel Xeon Phi processors (code name Knights Landing) that will empower the Cori supercomputer by the summer of 2016. “A key goal of the Cori Phase 1 system is to support the increasingly data-intensive computing needs of NERSC users. Toward this end, Phase 1 of Cori will feature more than 1,400 Intel Haswell compute nodes, each with 128 gigabytes of memory per node. The system will provide about the same sustained application performance as NERSC’s Hopper system, which will be retired later this year. The Cori interconnect will have a dragonfly topology based on the Aries interconnect, identical to NERSC’s Edison system.”

Video: Enabling Application Portability across HPC Platforms

“In this presentation, we will discuss several important goals and requirements of portable standards in the context of OpenMP. We will also encourage audience participation as we discuss and formulate the current state-of-the-art in this area and our hopes and goals for the future. We will start by describing the current and next generation architectures at NERSC and OLCF and explain how the differences require different general programming paradigms to facilitate high-performance implementations.”

With APEX, National Labs Collaborate to Develop Next-Gen Supercomputers

Today Los Alamos, Lawrence Berkeley, and Sandia national laboratories announced the Alliance for Application Performance at Extreme Scale (APEX). The new collaboration will focus on the design, acquisition and deployment of future advanced technology high performance computing systems.

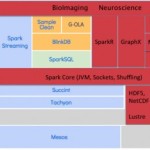

Cray, AMPLab, NERSC Collaborate on Spark Performance for HPC Platforms

Today NERSC announced a collaboration with UC Berkeley’s AMPLab and Cray to design large-scale data analytics stacks. “Analytics workloads will be an increasingly important workload on our supercomputers and we are thrilled to support and participate in this key collaboration,” said Ryan Waite, senior vice president of products at Cray. “As Cray’s supercomputing platforms enable researchers and scientists to model reality ever more accurately using high-fidelity simulations, we have long seen the need for scalable, performant analytic tools to interpret the resulting data. The Berkeley Data Analytics Stack (BDAS) and Spark, in particular, are emerging as a de facto foundation of such a toolset because of their combined focus on productivity and scalable performance.”

Users to Test DataWarp Burst Buffer on Cori Supercomputer

NERSC has selected a number of HPC research projects to participate in the center’s new Burst Buffer Early User Program, where they will be able to test and run their codes using the new Burst Buffer feature on the center’s newest supercomputer, Cori.

NERSC to Install Cori Phase 1 Supercomputer this Summer

Today NERSC announced that their Cori Phase 1 system will be the first supercomputer installed in the new Computational Research and Theory Facility, which is now in the final stages of construction at LBNL. Expected to be delivered this summer, the Cray XC40 supercomputer will be powered by Intel Haswell processors and Cray’s DataWarp burst buffer technology.