Maisons-Laffitte (France), Sept. 28, 2021 – SiPearl, whose mission is to design a high performance, low-power microprocessor for European exascale supercomputers, has opened a design center in Grenoble, France, with the goal of recruiting 50 engineers on site by the end of 2022. Following SiPeal facilities in Maisons-Laffitte, Duisburg, Barcelona and Sophia Antipolis, SiPearl’s Grenoble […]

Jean-Marc Denis Joins SiPearl as CSO

Maisons-Laffitte, France, 6 July 2021 – SiPearl, the designer of the microprocessor for the European exascale supercomputer, announced the appointment of Jean-Marc Denis as chief strategy officer. Previously, he was head of strategy, big data and security within the Atos group. Since 2018, he chaired the European Processor Initiative (EPI) consortium from which SiPearl was […]

SiPearl Says Rhea Exascale Chip Has Entered Accelerated Simulation Phase for 2022 Launch

SiPearl, the company designing the Rhea microprocessor for the European exascale supercomputer, announced it has passed a milestone before the chip’s scheduled 2022 launch. The company said it is moving into an “accelerated simulation phase” on the Veloce Strato hardware emulator from Siemens Digital Industries Software. SiPeal said the hardware emulation platform provides its chips […]

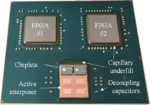

CEA Outlines Indigenous Path to European Exascale

CEA, the French Atomic Energy and Alternative Energy Commission, today presented what it said is a path to European exascale supercomputing utilizing technologies that combine “finer 3D interconnect paths for greater bandwidth between chiplets” within heterogenous nodes made up of generic processors. In an invited paper released at the IDEM 2020 (International Electron Devices Meeting) […]

European SiPearl Startup Licenses Arm for First-Generation Microprocessor

Today SiPearl, the company that is designing the high-performance, low-power microprocessor for the European exascale supercomputer, has signed a major technological licensing agreement with Arm, the global semiconductor IP provider. The agreement will enable SiPearl to benefit from the high-performance, secure, and scalable next-generation Arm Neoverse platform, codenamed ‶Zeusʺ, as well as leverage the robust software and hardware Arm ecosystem.

Exascale in Europe

Europe has developed a strategy for exascale computing, through partnerships and collaboration of European HPC vendors, academic institutions and HPC centers. It aims to deliver exascale-class systems and place the continent in the top three powers for supercomputing and science and industry using HPC. “It is a major step forward for Europe to reach the next level of computing capacity; it will help us to advance in future-oriented technologies, like the Internet of Things (Iot), AI, robotics and data analytics.”

European SiPearl Startup designing microprocessor for Exascale

Today European chip startup SiPearl announced it is moving into its operational phase. The company is now the 27th member of the European Processor Initiative (EPI) consortium. “By delivering supercomputing power, energy efficiency and backdoor-free security, the solutions that we are developing with support from the EPI members will enable Europe to gain its independence and, more importantly, to ensure its technological sovereignty on the market for high performance computing, which has become one of the key drivers for economic growth”, explains Philippe Notton, SiPearl’s CEO.

2020 HiPEAC Conference to Showcase European Computing Technologies

The 2020 HiPEAC conference will kick off next week in Bologna to showcase the innovative made-in-Europe technologies driving computing systems from the edge to the cloud. This year, the conference will dive into radical new developments in European processor technology, including open source hardware, while building on HiPEAC’s long-established reputation for cutting-edge research into heterogeneous architectures, cross-cutting artificial intelligence themes, security and more.

European Processor Initiative Reaches Important Milestones in First Year

The European Processor Initiative (EPI) has announced the completion of important milestones in its first year. “The first-generation chip family, named Rhea, will include Arm ZEUS architecture general purpose cores and prototypes of high energy-efficient accelerator tiles: RISC-V based (EPAC), Multi-Purpose Processing Array (MPPA), embedded FPGA (eFPGA) and cryptography HW engine. First Rhea chips will be fabricated in N6 technology aiming at the highest processing capabilities and energy efficiency.”

An Update on the European Processor Initiative

Jean-Marc Denis from EPI gave this talk at the HPC User Forum. “The EPI project aims to deliver a high-performance, low-power processor, implementing vector instructions and specific accelerators with high bandwidth memory access. The EPI processor will also meet high security and safety requirements. This will be achieved through intensive use of simulation, development of a complete software stack and tape-out in the most advanced semiconductor process node.”