“HBM is a new type of CPU/GPU memory (“RAM”) that vertically stacks memory chips, like floors in a skyscraper. In doing so, it shortens your information commute. Those towers connect to the CPU or GPU through an ultra-fast interconnect called the “interposer.” Several stacks of HBM are plugged into the interposer alongside a CPU or GPU, and that assembled module connects to a circuit board. Though these HBM stacks are not physically integrated with the CPU or GPU, they are so closely and quickly connected via the interposer that HBM’s characteristics are nearly indistinguishable from on-chip integrated RAM.”

Video: Altera’s Stratix 10 – 14nm FPGA Targeting 1GHz Performance

In this video from the 2015 Hot Chips Conference, Mike Hutton from Altera presents: Stratix 10 Altera’s 14nm FPGA Targeting 1GHz Performance. “Stratix 10 FPGAs and SoCs deliver breakthrough advantages in performance, power efficiency, density, and system integration: advantages that are unmatched in the industry. Featuring the revolutionary HyperFlex core fabric architecture and built on the Intel 14 nm Tri-Gate process, Stratix 10 devices deliver 2X core performance gains over previous-generation, high-performance FPGAs with up to 70% lower power.”

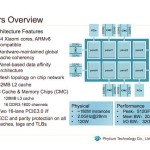

Video: Mars – A 64-Core ARMv8 Processor

In this video from the 2015 Hot Chips Conference, Charles Zhang from Phytium presents: Mars – A 64-Core ARMv8 Processor. Formed in China in 2012, Phytium is a unique technology provider of HPC servers, focusing mainly on high performance general microprocessor, accelerator chip, reference board design and various servers design from blade, cluster, standard stack to HPC Server. “Optimized for HPC, the Mars chip features eight panels, each with eight “Xiaomi” cores. The panels share an L2 cache of 32 MB, two Directory Control Units and a routing cell for the internal mesh.”