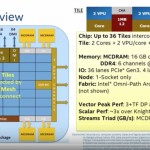

“The Intel’s next generation Xeon Phi processor family x200 product (code-name Knights Landing) brings in new memory technology, a high bandwidth on package memory called Multi-Channel DRAM (MCDRAM) in addition to the traditional DDR4. MCDRAM is a high bandwidth (~4x more than DDR4), low capacity (up to 16GB) memory, packaged with the Knights Landing Silicon. MCDRAM can be configured as a third level cache (memory side cache) or as a distinct NUMA node (allocatable memory) or somewhere in between. With the different memory modes by which the system can be booted, it becomes very challenging from a software perspective to understand the best mode suitable for an application.”

Video: Enabling Application Portability across HPC Platforms

“In this presentation, we will discuss several important goals and requirements of portable standards in the context of OpenMP. We will also encourage audience participation as we discuss and formulate the current state-of-the-art in this area and our hopes and goals for the future. We will start by describing the current and next generation architectures at NERSC and OLCF and explain how the differences require different general programming paradigms to facilitate high-performance implementations.”

Atos Launches Bull sequana X1000 Supercomputer

Today Atos launched the Bull sequana X1000, its new family of supercomputers on the company’s road to exascale. “The new Bull sequana system, powered by future Intel Xeon processors and the Intel Xeon Phi processor, code-named “Knights Landing”, is designed to address the performance, reliability and energy-efficiency requirements of exascale-class supercomputers,” said Raj Hazra, vice president and general manager, Enterprise and HPC Platforms Group, Intel Corporation. “We’re excited to be collaborating with Bull to bring to market this new generation of supercomputers on the path to exascale.”

CoolIT Systems to Showcase New Liquid Cooling Technologies at SC15

Today CoolIT Systems announced plans to showcase new server cooling technologies at the SC15 conference in Austin. Exhibiting at booth #163, CoolIT Systems will exhibit an expanded line of heat exchange solutions. Attendees will also find new customer case studies outlining the real-world benefits the industry is experiencing with liquid cooling.

Interview: Asetek Rides Rapid Adoption of Liquid Cooling for HPC

The HPC industry’s expanded use of liquid cooling was evident at the recent ISC 2015 conference in Frankfurt. To learn more, we caught up with Steve Branton from Asetek.

Coral and Intel’s Scalable System Framework – The Path to Exascale

“HPC has reached an inflection point with the convergence of traditional high performance computing and the emerging world of Big Data analytics. Intel’s HPC Scalable System Framework enables an unprecedented level of system balance, performance, and scalability necessary to meet the demands of bot compute- and data-intensive workloads, today and well into the future.”

Radio Free HPC Looks Back at ISC 2015

In this video, Dan Olds and Rich Brueckner from Radio Free HPC discuss the latest news in High Performance Computing from the ISC 2015 conference in Frankfurt, Germany.

HPC News Roundup for March 27, 2015

I’m on my way home from a series of Springtime HPC conferences with boatload of new videos and interviews on the latest in high performance computing. Here are some notable items that may have not made it to the front page.

Video: Preparing Your Application for Advanced Manycore Architectures

“Confronting power limitations and the high cost of data movement, new supercomputing architectures within the DOE are requiring users make changes to application codes to achieve high performance. More specifically, users will need to exploit greater on-node parallelism and longer vector units, and restructure code to take advantage of memory locality. In this presentation you will learn about coming architectural trends and what you can do now to start preparing your application.”

NERSC Leads Next-Generation Code Optimization Effort

“We are excited about launching NESAP in partnership with Cray and Intel to help transition our broad user base to energy-efficient architectures,” said Sudip Dosanjh, director of NERSC, the primary HPC facility for the DOE’s Office of Science. “We expect to see many aspects of Cori in an exascale computer, including dramatically more concurrency and on-package memory. The response from our users has been overwhelming—they recognize that Cori will allow them to do science that can’t be done on today’s supercomputers.”