Last week we detailed recent rumors that Intel was getting back into the HPC pool. Well, they officially lifted the curtain on the first set of plans this morning at ISC. According to their release, the have a new codename for the project: “Knights Corner.”

Last week we detailed recent rumors that Intel was getting back into the HPC pool. Well, they officially lifted the curtain on the first set of plans this morning at ISC. According to their release, the have a new codename for the project: “Knights Corner.”

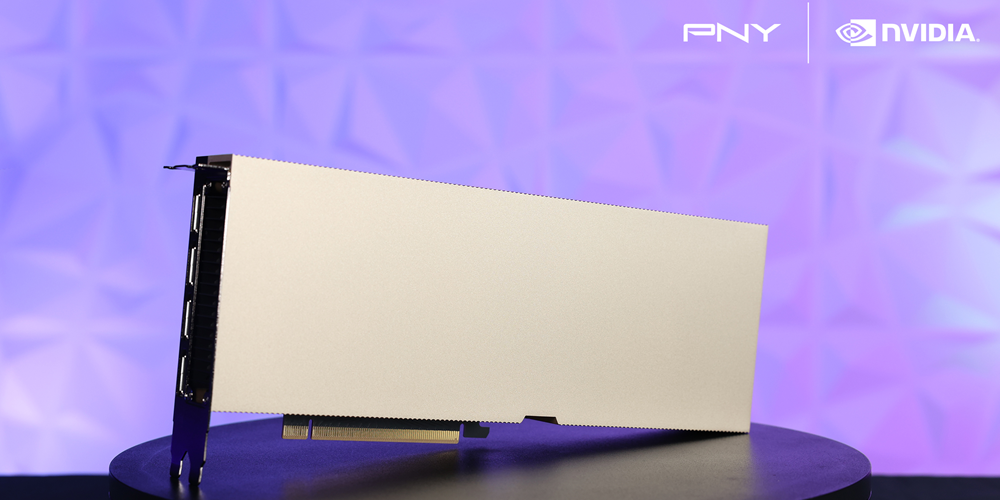

The new product will feature Intel’s 22nm technology and scale up to 50 cores in a socket. The release quotes Knights Corner sharing the Intel core technology, programming methods and software tools. This implies x86_64 and Intel’s suite of threading tools such as the Thread Building Blocks and the recent Cilk++ acquisition.

Intel’s Xeon processors, and now our new Intel(R) Many Integrated Core architecture products, will further push the boundaries of science and discovery as Intel accelerates solutions to some of humanity’s most challenging problems,” said Kirk Skaugen, vice president and general manager of Intel’s Data Center Group. “The Intel(R) MIC architecture will extend Intel’s leading HPC products and solutions that are already in nearly 82 percent of the world’s top supercomputers. Today’s investments are indicative of Intel’s growing commitment to the global HPC community.”

Select developers are already on the receiving end of the development kits for the project, codenamed “Knights Ferry.” Intel will expand the range of developer tools later this year. The architecture as a whole is being called Intel MIC and shares a direct pedigree with Larrabee.

The CERN openlab team was able to migrate a complex C++ parallel benchmark to the Intel MIC software development platform in just a few days,” said Sverre Jarp, CTO of CERN openlab. “The familiar hardware programming model allowed us to get the software running much faster than expected.”

For more info, read Intel’s full writeup here.

[…] that precedes the Knights Corner chip. Both are part of the Many Integrated Core (MIC) architecture announced in May; Knights Ferry was briefed by Kirk Skaugen […]