Intel today officially announced its long awaited, next-generation server chips: the Xeon CPU Max, known to date as “Sapphire Rapids,” and the Data Center GPU Max, which for more than two years has been known – and been a focal point of scrutiny, speculation and frustration – as “Ponte Vecchio.”

Intel today officially announced its long awaited, next-generation server chips: the Xeon CPU Max, known to date as “Sapphire Rapids,” and the Data Center GPU Max, which for more than two years has been known – and been a focal point of scrutiny, speculation and frustration – as “Ponte Vecchio.”

Both chips have been delayed, the GPU in particular, and both have taken on outsized prominence in the HPC industry because they will power Intel’s Aurora supercomputer, one the U.S.’s first three exascale-class systems now being installed at Argonne National Laboratory. Intel said in late September it had begun shipping Aurora blades (this reporter saw installed blades at Argonne’s Leadership Computing Facility earlier this week, see below image), making Argonne one of the first customers to be granted access to the new processors. Intel said Aurora – to be comprised of 10,000 blades, each with six Max GPUs and two Max CPUs – is expected to exceed 2 exaFLOPS peak double-precision performance.

In its announcement today, Intel said the Max Series products are slated to launch in January 2023.

The Xeon Max CPU is the first x86-based chip with high bandwidth memory (HBM), which the company said accelerates many HPC workloads without the need for code changes. The Max Series GPU is Intel’s highest density processor, packing more than 100 billion transistors into a 47-tile package with up to 128 gigabytes of high bandwidth memory.

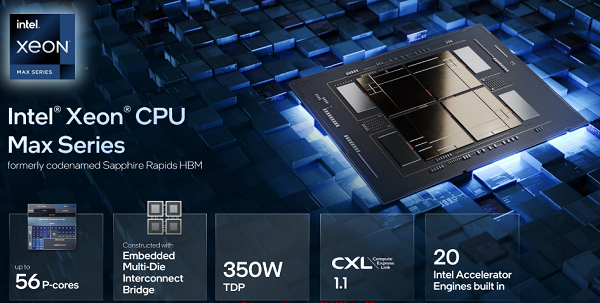

The Xeon Max CPU offers up to 56 performance cores constructed of four tiles and connected using Intel’s embedded multi-die interconnect bridge (EMIB) technology, in a 350-watt envelope. It contains 64GB of high bandwidth in-package memory, as well as PCI Express 5.0 and CXL1.1 I/O. Xeon Max CPUs will provide more than 1GB of high bandwidth memory (HBM) capacity per core, enough to fit most common HPC workloads, according to Intel, and up to 4.8x better performance compared to the competition on HPC workloads, the company said.

Intel “Sapphire Rapids” CPU Max

Intel said the new CPU has 68 percent less power usage than competing product for the same HCPG performance and that AMX extensions boost AI performance and deliver 8x peak throughput over AVX-512 for INT8 with INT32 accumulation operations.

The Max Series GPUs deliver up to 128 Xe-HPC cores, which Intel called “the new foundational architecture” for demanding workloads. The GPU series features, according to Intel, 408MB of L2 cache – the highest in the industry, according to the company – and 64MB of L1 cache. Intel said it’s only HPC/AI GPU with native ray tracing acceleration, for scientific visualization and animation.

Intel “Ponte Vecchio” Data Center GPU Max

Max Series GPUs will be available in several form factors:

-

-

- Max Series 1100 GPU: A 300-watt double-wide PCIe card with 56 Xe cores and 48GB of HBM2e memory. Multiple cards can be connected via Intel Xe Link bridges.

-

- Max Series 1350 GPU: A 450-watt OAM module with 112 Xe cores and 96GB of HBM.

- Max Series 1550 GPU: Intel’s maximum performance 600-watt OAM module with 128 Xe cores and 128GB of HBM.

Intel said it also will offer the Data Center GPU Max subsystem with x4 GPU OAM carrier board and Intel Xe Link to enable multi-GPU communication within the subsystem.

Intel also said its 2023 oneAPI software ecosystem will provide a single programming environment for both processors and that oneAPI combined with AI tools “will deliver capabilities to enable the Intel Max Series products’ advanced features.”

In advance of SC22, Argonne and Intel unveiled Sunspot, Aurora’s Test Development System consisting of 128 production blades. Researchers from the Aurora Early Science Program will have access to the system beginning in late this year.

Intel said the Max Series products will power several other HPC systems critical for national security and basic research, including Crossroads at Los Alamos National Laboratory, CTS-2 systems at Lawrence Livermore National Laboratory and Sandia National Laboratory, and Camphor3 at Kyoto University.

Aurora blade at Argonne

Looking ahead, Intel said the upcoming “Rialto Bridge” Data Center Max Series GPU is intended to arrive in 2024. The company added that “Intel is then planning to release the next major architecture innovation to enable the future of HPC. The company’s upcoming XPU, code-named Falcon Shores, will combine Xe and x86 cores on a single package.” This new architecture will have the flexibility to integrate new IPs from Intel and customers, manufactured using Intel’s IDM 2.0 model, the company said.

“To ensure no HPC workload is left behind, we need a solution that maximizes bandwidth, maximizes compute, maximizes developer productivity and ultimately maximizes impact,” said Jeff McVeigh, Intel corporate vice president and general manager, Super Compute Group. “The Intel Max Series product family brings high bandwidth memory to the broader market, along with oneAPI, making it easy to share code between CPUs and GPUs and solve the world’s biggest challenges faster.”