[SPONSORED CONTENT] High performance computing (HPC) often sets trends for the data center. Driving innovation, adding new functionality, and enabling simulations to deliver more accuracy, finer details, and insights. Recently AMD released four new AMD EPYC™ 7003 Series processors with AMD 3D V-Cache™ technology. Socket compatible with existing EPYC 7003 processors, the AMD 3D V-Cache triples the amount of available L3 cache to 768MBs per socket versus standard EPYC 7003 series processors, giving you additional flexibility when choosing the right processor for your workloads.

[SPONSORED CONTENT] High performance computing (HPC) often sets trends for the data center. Driving innovation, adding new functionality, and enabling simulations to deliver more accuracy, finer details, and insights. Recently AMD released four new AMD EPYC™ 7003 Series processors with AMD 3D V-Cache™ technology. Socket compatible with existing EPYC 7003 processors, the AMD 3D V-Cache triples the amount of available L3 cache to 768MBs per socket versus standard EPYC 7003 series processors, giving you additional flexibility when choosing the right processor for your workloads.

The best gets better. Building on top of the world record setting EPYC family of processors[1], this latest set of processors was specifically designed to provide significant performance uplifts for workloads that are cache sensitive, like computational fluid dynamics (CFD), Electronic Design Automation (EDA), Structural Analysis and Finite Element Analysis (FEA). The larger L3 cache enables critical data to be closer to the cores, which can reduce latency and increase bandwidth to that information.

To break it down further, each Core Complex Die (CCD) has 96MB of L3 cache on the 3rd Gen EPYC with AMD 3D V-Cache, providing the “Zen 3” cores faster access to low latency memory without having to access the main memory outside of the CPU. This means more of your application’s dataset can sit closer to the core that is using that data without having to reach out to main memory. And because this is an enhancement to existing EPYC 7003 processor architecture, out of the box your applications can take advantage of the additional L3 cache.

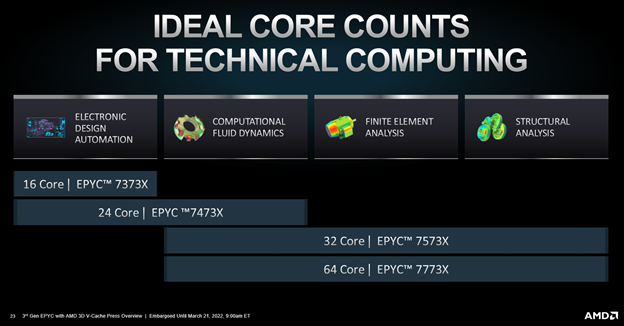

The 4 new offerings are designed with technical computing applications in mind. Each with suggested workload affinity. EDA applications are typically lightly threaded. They benefit from a larger cache per core ratio and increased memory bandwidth. Meanwhile CFD, FEA and structural analysis applications tend to be highly threaded and use data set sizes that can take advantage of the increased cache per core density. In Figure 1 we align these general application characteristics to suggested processors.

Figure 1: Ideal core counts

How do you know if your application may be able to take advantage of the additional L3 cache that these new SKUs offer? Does your application have high L3 cache misses or a working data set size that’s smaller than the L3 cache (or, larger but often re-used between cores)? These are all great signs that your workload can potentially benefit from AMD 3D V-Cache. Home-grown applications that do not have these characteristics but could potentially make use of increased memory bandwidth or reduced memory latency could be updated and optimized to utilize more L3 cache. In contrast, there are many off the shelf applications that need no changes at all and can take advantage of AMD 3D V-Cache. A great example in the EDA space is RTL simulation (Register-transfer level). RTL simulation makes up the majority of the work in digital circuit simulation workflow. In AMD testing, using the 16-core 3rd Gen AMD EPYC processor with AMD 3D V-Cache accelerated RTL simulation by up to 66% over standard 3rd Gen AMD EPYC processors.[2]

AMD is charting a bold path to advanced energy efficiency. Because of the “EPYC” jump in performance AMD 3D V-Cache offers certain workloads, you may need fewer servers to accomplish the same amount of work. This can reduce your rack space usage and power consumption because you don’t need as many systems to get the same amount of work done. The physics of AMD 3D V-Cache hybrid bonding technology is also an inherent thermal benefit when compared to Micro Bump 3D technology. Utilizing the industry’s first logical stacking based on a copper-to-copper hybrid bonding “bumpless” chip-on-wafer process enables more than 15 times interconnect density[3] and more than 3X interconnect energy efficiency[4].

How can your organization benefit from 1.5GB of L3 cache? Speak with your AMD, OEM or HPC partner to learn more. www.amd.com/epyc3x

Footnote:

- 1) EPYC-022A: For a complete list of world records see http://amd.com/worldrecords.

- 3) EPYC-026: Based on calculated areal density and based on bump pitch between AMD hybrid bond AMD 3D V-Cache stacked technology compared to AMD 2D chiplet technology and Intel 3D stacked micro-bump technology.

- 4) EPYC-027: Based on AMD internal simulations and published Intel data on “Foveros” technology specifications.

- 2) MLNX-001A: EDA RTL Simulation comparison based on AMD internal testing completed on 9/20/2021 measuring the average time to complete a test case simulation. comparing: 1x 16C EPYC™ 7373X with AMD 3D V-Cache Technology versus 1x 16C AMD EPYC™ 73F3 on the same AMD “Daytona” reference platform. Results may vary based on factors including silicon version, hardware and software configuration and driver versions.

[1] EPYC-022A: For a complete list of world records see http://amd.com/worldrecords

[2] MLNX-001A

[3] EPYC-026

[4] EPYC-027