In this slidecast, Mike Black from Micron describes the company’s Hybrid Memory Cube technology for the next-generation Xeon Phi processor, codenamed Knights Landing. The memory solution is the result of a long-term effort between the two companies to break down the memory wall, leveraging the fundamental DRAM and stacking technologies also found in Micron’s Hybrid Memory Cube products.

The ecosystem is changing and the importance of scalable on-package memory and memory bandwidth is now coming to light,” said Chirag Dekate, Research Manager at IDC. “Memory is at the heart of the solution space which will benefit both big compute and big data. This announcement is a clear validation of how Micron is advancing the role and impact of memory on systems and the value that 3D memory can deliver.”

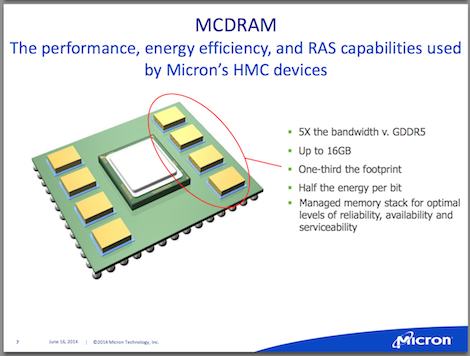

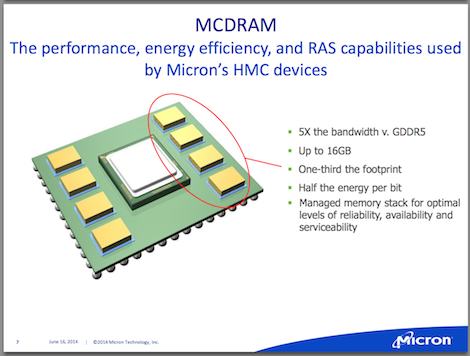

Delivering 5X the sustained memory bandwidth versus DDR4 with one-third the energy per bit in half the footprint, the Knights Landing high performance, on package memory combines high-speed logic and DRAM layers into one optimized package that will set a new industry benchmark for performance and energy efficiency. The memory stack provides optimal levels of reliability, availability, and serviceability, which are critical elements for high-performance computing systems. One of the first applications of the Knights Landing system—a next-generation Cray XC supercomputer—was announced by NERSC on April 29.

The next-generation Intel Xeon Phi processor, codenamed Knights Landing, will launch with up to 16GB of high performance, on-package memory that delivers over 5x the sustained memory bandwidth versus DDR4 and brings tremendous power-efficiency and space-savings. It is the first Intel HPC processor to use this new high performance on-package memory,” said Charles Wuischpard, Vice President, General Manager, Workstations and High Performance Computing Data Center Group at Intel. “This will allow the world’s leading researchers, scientists, and engineers to run larger workloads faster while maintaining current code investments. We’re pleased to be working with Micron to deliver it.”