In this special guest feature from the SC19 Blog, Charity Plata from Brookhaven National Lab catches up with Dr. Lin Gan from Tsinghua University, who’s outstanding work in HPC has been recognized with a number of awards including the Gordon Bell Prize. As a highly awarded young researcher who already has been acknowledged for “outstanding, influential, and potentially long-lasting contributions” in HPC, Gan shares his thoughts on future supercomputers and what it means to say, “HPC Is Now.”

Interview: Why HPC is the Right Tool for Physics

Over at the SC19 Blog, Charity Plata continues the HPC is Now series of interviews with Enrico Rinaldi, a physicist and special postdoctoral fellow with the Riken BNL Research Center. This month, Rinaldi discusses why HPC is the right tool for physics and shares the best formula for garnering a Gordon Bell Award nomination. “Sierra and Summit are incredible machines, and we were lucky to be among the first teams to use them to produce new scientific results. The impact on my lattice QCD research was tremendous, as demonstrated by the Gordon Bell paper submission.”

Gordon Bell Prize Highlights the Impact of Ai

In this special guest feature from Scientific Computing World, Robert Roe reports on the Gordon Bell Prize finalists for 2018. “The finalist’s research ranges from AI to mixed precision workloads, with some taking advantage of the Tensor Cores available in the latest generation of Nvidia GPUs. This highlights the impact of AI and GPU technologies, which are opening up not only new applications to HPC users but also the opportunity to accelerate mixed precision workloads on large scale HPC systems.”

5 of 6 Gordon Bell Finalists use NVIDIA Volta Tensor Core GPUs

Over at the NVIDIA Blog, Geetika Gupta writes that the company’s powerful GPUs are being used by five of the six Gordon Bell Prize finalists. Just announced by ACM, these world-leading researchers did their work on the new NVIDIA GPU-accelerated Summit system at Oak Ridge National Laboratory and Sierra system at Lawrence Livermore National Laboratory.

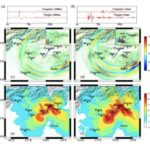

Lessons on Integrating and Utilizing 10 Million Cores: Experience of Sunway TaihuLight

Haohuan Fu gave this Invited Talk at SC17 in Denver. “The Sunway TaihuLight supercomputer is the world’s first system with a peak performance greater than 100 PFlops and a parallel scale of over 10 million cores. Different from other existing heterogeneous supercomputers, the system adopts its unique design strategies in both the architecture of its 260-core Shenwei CPU and its way of integrating 40,960 such CPUs as 40 powerful cabinets. This talk will first introduce and discuss design philosophy about the approach to integrate these 10 million cores, at both the processor and the system level.”

SC17 Invited Talk: Gordon Bell on the Rise of Scalable Systems

Gordon Bell gave this Invited Talk at SC17. “A globally recognized pioneer in the supercomputing world, Bell will be sharing his latest reflections and insights with his fellow scientists, engineers and researchers at SC17 in Denver. Bell will highlight the work of the winners of the ACM Gordon Bell Prize from the past 30 years. Presented by the ACM, the recipients’ achievements have chronicled the important innovations and transitions of high performance computing, including the rise of parallel computing, a computing architecture that breaks down problems into smaller ones that may be solved simultaneously.”

SDSC Earthquake Codes Used in 2017 Gordon Bell Prize Research

A Chinese team of researchers awarded this year’s prestigious Gordon Bell prize for simulating the devastating 1976 earthquake in Tangshan, China, used an open-source code developed by researchers at the San Diego Supercomputer Center (SDSC) at UC San Diego and San Diego State University (SDSU) with support from the Southern California Earthquake Center (SCEC). “We congratulate the researchers for their impressive innovations porting our earthquake software code, and in turn for advancing the overall state of seismic research that will have far-reaching benefits around the world,” said Yifeng Cui, director of SDSC’s High Performance Geocomputing Laboratory, who along with SDSU Geological Sciences Professor Kim Olsen, Professor Emeritus Steven Day and researcher Daniel Roten developed the AWP-ODC code.

Gordon Bell Prize Finalists to Present their work at SC17

SC17 has announced the finalists for the Gordon Bell Prize in High Performance Computing. The $10,000 prize will be presented to the winner at the conference in Denver next month. “The Gordon Bell Prize recognizes the extraordinary progress made each year in the innovative application of parallel computing to challenges in science, engineering, and large-scale data analytics. Prizes may be awarded for peak performance or special achievements in scalability and time-to-solution on important science and engineering problems.”

Computing Pioneer Gordon Bell to Present at SC17

Computing Pioneer Gordon Bell will share insights and inspiration at SC17 in Denver. “We are honored to have the legendary Gordon Bell speak at SC17,” said Conference Chair Bernd Mohr, from Germany’s Jülich Supercomputing Centre. “The prize he established has helped foster the rapid adoption of new paradigms, given recognition for specialized hardware, as well as rewarded the winners’ tremendous efforts and creativity – especially in maximizing the application of the ever-increasing capabilities of parallel computing systems. It has been a beacon for discovery and making the ‘might be possible’ an actual reality.”

PASC17 to Feature Talk by Gordon Bell Prize Winner Haohuan Fu

“This talk reports efforts on refactoring and optimizing the climate and weather forecasting programs – CAM and WRF – on Sunway TaihuLight. To map the large code base to the millions of cores on the Sunway system, OpenACC-based refactoring was taken as the major approach, with source-to-source translator tools applied to exploit the most suitable parallelism for the CPE cluster and to fit the intermediate variable into the limited on-chip fast buffer.”