Funded by the European Commission in 2011, the DEEP project was the brainchild of scientists and researchers at the Jülich Supercomputing Centre (JSC) in Germany. The basic idea is to overcome the limitations of standard HPC systems by building a new type of heterogeneous architecture. One that could dynamically divide less parallel and highly parallel parts of a workload between a general-purpose Cluster and a Booster—an autonomous cluster with Intel® Xeon Phi™ processors designed to dramatically improve performance of highly parallel code.

Archives for March 2016

Intrinsic Vectorization for Intel Xeon Phi

“It is important to be able to express algorithms and then the coding in an architecture independent manner to gain maximum portability. Vectorization, using the available CPUs and coprocessors such as the Intel Xeon Phi coprocessor, are critical for HPC applications where performance is of the highest importance. However, since architectures change over time and become more powerful, using libraries that can adjust to the new architectures is quite important.”

Co-Design Architecture: Emergence of New Co-Processors

“High performance computing has begun scaling beyond Petaflop performance towards the Exaflop mark. One of the major concerns throughout the development toward such performance capability is scalability – at the component level, system level, middleware and the application level. A Co-Design approach between the development of the software libraries and the underlying hardware can help to overcome those scalability issues and to enable a more efficient design approach towards the Exascale goal.”

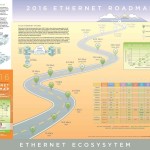

A Quick Look at the 2016 Ethernet Roadmap

Today the Ethernet Alliance unveiled its 2016 Ethernet Roadmap at OFC 2016. The roadmap highlights Ethernet’s breadth of speeds, current and next-generation modules and interfaces, PoE, and innovations like the OIF’s FlexEthernet, and offers an overview of existing and future modules including QSFP-DD, microQSFP, and OBO; interfaces; and nomenclature at speeds from 10 Mb/s to 400GbE.

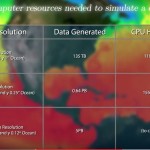

Supercomputing Extreme Weather Events and Climate Change

A recent study conducted by the Barcelona Supercomputer Center suggests that calibrated model ensembles improve the trustworthiness of climate event attribution to extreme weather events. The study also found that current climate model limitations tend to overestimate climate change attribution.

Video: The Nvidia Tesla Accelerated Computing Platform

Axel Koehler from Nvidia presented this talk at the HPC Advisory Council Switzerland Conference. “Accelerated computing is transforming the data center that delivers unprecedented throughput, enabling new discoveries and services for end users. This talk will give an overview about the NVIDIA Tesla accelerated computing platform including the latest developments in hardware and software. In addition it will be shown how deep learning on GPUs is changing how we use computers to understand data.”

Seeking Students and Instructors for the Blue Waters Intro to HPC Virtual Course

The Blue Waters project at the University of Illinois is offering a new graduate course entitled Introduction to High Performance Computing. The course will be offered as a collaborative, online course for multiple participating institutions fall semester 2016. “The project is seeking university partners that are interested in offering the course for credit to their students. The course includes online video lectures, quizzes, and homework assignments with access to free accounts on the Blue Waters system.”

Cooling Today’s Hot New Processors

Expected later in 2016, Intel will be releasing production versions of its Knights Landing (KNL) 72-core coprocessor. These next generation coprocessors are impacting the physical design of the supercomputers now coming down the pike in a number of ways. One of the most dramatic changes is the significant increase in cooling requirements – these are high wattage chips that run very hot and present some interesting engineering challenges for systems designers.

Intel MPI Messaging Paper Wins ISC 2016 Hans Meuer Award

Today ISC 2016 announced that a research paper in the area of Message Passing Interface (MPI) performance, has been selected to receive the 2016 Hans Meuer Award. The awarding will take place at the ISC High Performance conference on Monday, June 20.

Tutorial on Deep Learning

Zaikun Xu from the Università della Svizzera Italiana presented this talk at the Switzerland HPC Conference. “In the past decade, deep learning as a life-changing technology, has gained a huge success on various tasks, including image recognition, speech recognition, machine translation, etc. Pioneered by several research groups, Deep learning is a renaissance of neural network in the Big data era.”