Today Gidel announced a new compression IP and a renewed focus on compression and encryption algorithms for the HPC and Vision markets. The compression algorithm requires extremely low power, encoding more than 1 GB/sec utilizing just 1% of the FPGA, thus opening up new possibilities for data centers in particular. “Real-time compression capability provides a number of advantages in storage and efficiency,” notes Ofer Pravda, VP Marketing & Sales at Gidel. “Compressed data can be stored in real-time, as opposed to systems that store the raw data and then compress offline at a later date.”

Intel to Showcase AI and HPC Demos at ISC 2018

Today Intel released a sneak peek at their plans for ISC 2018 in Frankfurt. The company will showcase how it’s helping AI developers, data scientists and HPC programmers transform industries by tapping into HPC to power the AI solutions. “ISC brings together academic and commercial disciplines to share knowledge in the field of high performance computing. Intel’s presence at the event will include keynotes, sessions, and booth demos that will be focused on the future of HPC technology, including Artificial Intelligence (AI) and visualization.”

Call For Presentations: MVAPICH User Group Meeting (MUG 2018)

The MVAPICH User Group Meeting (MUG 2018) has issued its Call For Presentations. The event will take place from August 6-8 in Columbus, Ohio. “MUG aims to bring together MVAPICH2 users, researchers, developers, and system administrators to share their experience and knowledge and learn from each other. The event includes Keynote Talks, Invited Tutorials, Invited Talks, Contributed Presentations, Open MIC session, hands-on sessions MVAPICH developers, etc.”

Unified Deep Learning Configurations and Emerging Applications

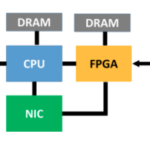

This is the final post in a five-part series from a report exploring the potential machine and a variety of computational approaches, including CPU, GPU and FGPA technologies. This article explores unified deep learning configurations and emerging applications.

Unified Deep Learning with CPU, GPU and FPGA Technologies

Deep learning and complex machine learning has quickly become one of the most important computationally intensive applications for a wide variety of fields. Download the new paper — from Advanced Micro Devices Inc. (AMD) and Xilinx Inc. — that explores the challenges of deep learning training and inference, and discusses the benefits of a comprehensive approach for combining CPU, GPU, FPGA technologies, along with the appropriate software frameworks in a unified deep learning architecture.

FPGA Programming Made Easy

In the past, it was necessary to understand a complex programming language such as Verilog or VHDL, that was designed for a specific FPGA. “Using a familiar language such as OpenCL, developers can become more productive, sooner when deciding to use an FPGA for a specific purpose. OpenCL is portable and is designed to be used with almost any type of accelerator.”

HPC Processor Competition Heats Up

In this special guest feature, Robert Roe from Scientific Computing World explores efforts to diversify the HPC processor market. “With the arrival of Arm and now the reintroduction of AMD to HPC, there are signs of new life in an HPC processor market that has been dominated by Intel Xeon processors for a number of years.”

Enabling FPGAs

Field Programmable Gate Arrays (FPGAs) are an exciting technology that allows hardware designers to create new digital circuits through a programming environment. Compared to hardware that is designed once or software which must adhere to the hardware architecture, an FPGA allows developers to draw a circuit to solve a specific problem.

New TeraBox 1U FPGA Server Doubles Compute and I/O Density

Today BittWare announced the TeraBox 1432D high density 1U FPGA server at SC17. Based on a Dell PowerEdge C4130, the customized TeraBox 1432D provides an unprecedented thirty-two 100GbE ports directly connected to four large Xilinx or Intel FPGAs on BittWare accelerator cards. This server targets users requiring the highest density of large FPGAs with directly-connected I/O for clustering or networking.

Gidel Launches Acceleration Boards Based on Intel Stratix 10 FPGAs

Today Gidel launched their Proc10S family of high performance, scalable compute acceleration boards. The devices are based on the Stratix 10 FPGA, which was released by Intel in late 2016. “Gidel’s newest acceleration board was designed with high density Big Data and HPC applications in mind. “The Proc10S is a heavy-duty FPGA and thus opens new markets in HPC for Gidel, such as Deep Learning and Big Data analytics,” says Ofer Pravda, VP Marketing and Sales at Gidel. “Gidel’s long history in algorithm acceleration utilizing FPGA technology has resulted in an enormous wealth of product knowledge that provides us with an advantage in certain HPC and Vision arenas.”