“Bret Costelow is an inspiring sales leader with a clear understanding of our customers’ needs and a vision of how DDN’s technologies and solutions can best solve their toughest data storage challenges,” said Robert Triendl, senior vice president, global sales, marketing, and field services, DDN. “Bret’s proven success in high-growth business settings, deep knowledge of the Lustre* and HPC market, proven track record for generating traction with innovative, advanced technologies, and his broad experience with software sales make him a great asset to our team and a great resource for our partners and customers around the world.”

ORNL Creates Programming System for NVM Main Memory Systems

Researchers at the Future Technologies Group at Oak Ridge National Laboratory (ORNL) have developed a novel programming system that extends C with intuitive, language-level support for programming NVM as persistent, high-performance main memory; the prototype system is named NVL-C.

Satoshi Matsuoka Presents: The Inevitable End of Moore’s Law

“The promising new parameter in place of the transistor count is the perceived increase in the capacity and bandwidth of storage, driven by device, architectural, as well as packaging innovations: DRAM-alternative Non-Volatile Memory (NVM) devices, 3-D memory and logic stacking evolving from VIAs to direct silicone stacking, as well as next-generation terabit optics and networks. The overall effect of this is that, the trend to increase the computational intensity as advocated today will no longer result in performance increase, but rather, exploiting the memory and bandwidth capacities will instead be the right methodology.”

DDN Reports Growing Momentum Leading into SC15

Today DDN announced the highest bookings quarter in the company’s history with double-digit year-over-year growth.

Radio Free HPC Looks at 3D XPoint Non-Volatile Memory

In this video, the Radio Free HPC team looks at the newly announced 3D XPoint technology from Intel and Micron. “3D XPoint ushers in a new class of non-volatile memory that significantly reduces latencies, allowing much more data to be stored close to the processor and accessed at speeds previously impossible for non-volatile storage.”

Intel and Micron Announce 3D XPoint Non-Volatile Memory

Today Intel Corporation and Micron Technology unveiled 3D XPoint technology, a non-volatile memory that has the potential to revolutionize any device, application or service that benefits from fast access to large sets of data. Now in production, 3D XPoint technology is a major breakthrough in memory process technology and the first new memory category since the introduction of NAND flash in 1989.

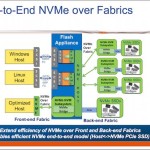

Video: NVM Express Introduction and Tutorial

NVM Express is a specification for accessing solid-state drives (SSDs) attached through the PCI Express (PCIe) bus. “NVM” stands as an acronym for non-volatile memory, which is used in SSDs. As a logical device interface, NVM Express has been designed from the ground up, capitalizing on the low latency and parallelism of PCI Express SSDs, and mirroring the parallelism of contemporary CPUs, platforms and applications. By allowing parallelism levels offered by SSDs to be fully utilized by host’s hardware and software, NVM Express brings various performance improvements.

Video: Application Experiences on DDN’s IME Burst Buffer

“The DDN Infinite Memory Engine (IME) unleashes a new I/O provisioning paradigm. This breakthrough, software defined storage application introduces a whole new new tier of transparent, extendable, non-volatile memory (NVM), that provides game-changing latency reduction and greater bandwidth and IOPS performance for the next generation of performance hungry scientific, analytic and big data applications – all while offering significantly greater economic and operational efficiency than today’s traditional disk-based and all flash array storage approaches that are currently used to scale performance.”

Video: Prototyping Byte-Addressable NVM Access

In this video from the 2015 OFS Developer’s Workshop, Bernard Metzler presents: Prototyping Byte-Addressable NVM Access.

Open Fabrics Workshop to Focus on Application Performance, NVM, and SoCs

Today the Open Fabrics Alliance announced that their upcoming International OFS Developers’ Workshop will center around three major themes: Applications Performance, Non-Volatile Memory, and Systems-on-a-Chip (SoCs).